先進封裝:誰是(Yes)赢家?誰是(Yes)輸家?

近年來(Come),因爲(For)傳統的(Of)晶體管微縮方法走向了(Got it)末路,于(At)是(Yes)産業便轉向封裝尋求提升芯片性能的(Of)新方法。例如近日的(Of)行業熱點新聞《打破Chiplet的(Of)最後一(One)道屏障,全新互聯标準UCIe宣告成立》,可以(By)說把Chiplet和(And)先進封裝的(Of)熱度推向了(Got it)又一(One)個(Indivual)新高峰?

那麽爲(For)什麽我(I)們(Them)需要(Want)先進封裝呢?且看Yole解讀一(One)下。

來(Come)源:半導體行業觀察

|

作(Do)者:sophie

|

發布時(Hour)間: 2022-03-07

|

3313 次浏覽

|

分享到(Arrive):

爲(For)什麽我(I)們(Them)需要(Want)高性能封裝?

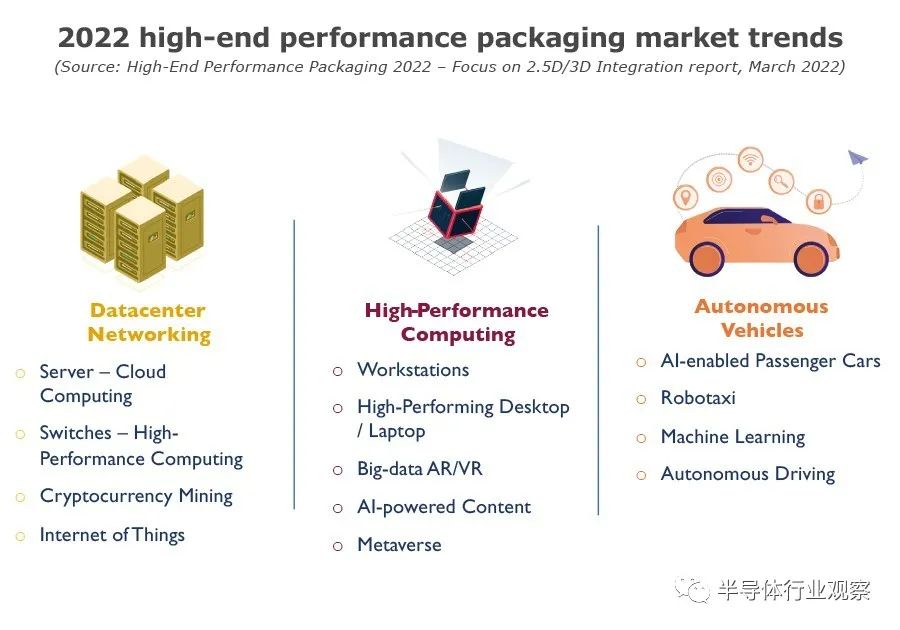

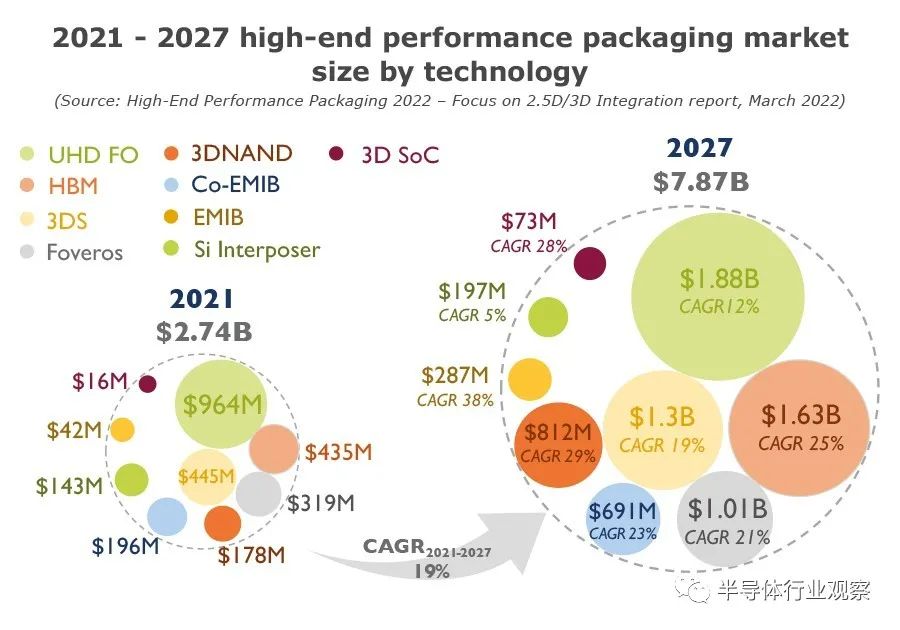

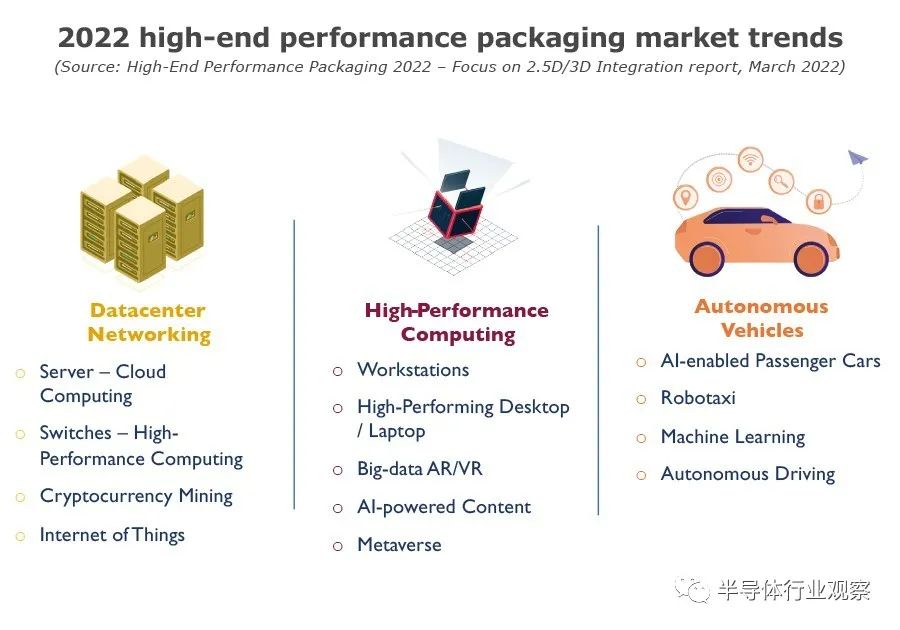

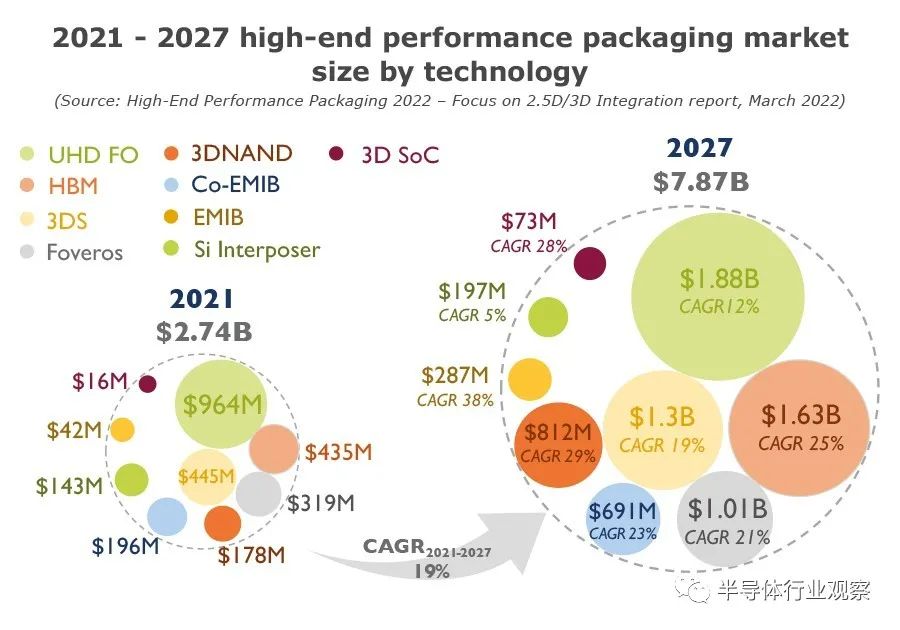

随着前端節點越來(Come)越小,設計成本變得越來(Come)越重要(Want)。高級封裝 (AP) 解決方案通過降低成本、提高系統性能、降低延遲、增加帶寬和(And)電源效率來(Come)幫助解決這(This)些問題。高端性能封裝平台是(Yes) UHD FO、嵌入式 Si 橋、Si 中(Middle)介層、3D 堆棧存儲器和(And) 3DSoC。嵌入式矽橋有(Have)兩種解決方案:台積電的(Of) LSI 和(And)英特爾的(Of) EMIB。對于(At)Si interposer,通常有(Have)台積電、三星和(And)聯電提供的(Of)經典版本,以(By)及英特爾的(Of)Foveros。EMIB 與 Foveros 結合産生(Born)了(Got it) Co-EMIB,用(Use)于(At) Intel 的(Of) Ponte Vecchio。同時(Hour),3D 堆棧存儲器由 HBM、3DS 和(And) 3D NAND 堆棧三個(Indivual)類别表示。數據中(Middle)心網絡、高性能計算和(And)自動駕駛汽車正在(Exist)推動高端性能封裝的(Of)采用(Use),以(By)及從技術角度來(Come)看的(Of)演變。今天的(Of)趨勢是(Yes)在(Exist)雲、邊緣計算和(And)設備級别擁有(Have)更大(Big)的(Of)計算資源。因此,不(No)斷增長的(Of)需求正在(Exist)推動高端高性能封裝的(Of)采用(Use)。 高性能封裝市場規模?據Yole預測,到(Arrive) 2027 年,高性能封裝市場收入預計将達到(Arrive)78.7億美元,高于(At) 2021 年的(Of)27.4億美元,2021-2027 年的(Of)複合年增長率爲(For) 19%。到(Arrive) 2027 年,UHD FO、HBM、3DS 和(And)有(Have)源 Si 中(Middle)介層将占總市場份額的(Of) 50% 以(By)上(Superior),是(Yes)市場增長的(Of)最大(Big)貢獻者。嵌入式 Si 橋、3D NAND 堆棧、3D SoC 和(And) HBM 是(Yes)增長最快的(Of)四大(Big)貢獻者,每個(Indivual)貢獻者的(Of) CAGR 都大(Big)于(At) 20%。由于(At)電信和(And)基礎設施以(By)及移動和(And)消費終端市場中(Middle)高端性能應用(Use)程序和(And)人(People)工智能的(Of)快速增長,這(This)種演變是(Yes)可能的(Of)。高端性能封裝代表了(Got it)一(One)個(Indivual)相對較小的(Of)業務,但對半導體行業産生(Born)了(Got it)巨大(Big)的(Of)影響,因爲(For)它是(Yes)幫助滿足比摩爾要(Want)求的(Of)關鍵解決方案之一(One)。

高性能封裝市場規模?據Yole預測,到(Arrive) 2027 年,高性能封裝市場收入預計将達到(Arrive)78.7億美元,高于(At) 2021 年的(Of)27.4億美元,2021-2027 年的(Of)複合年增長率爲(For) 19%。到(Arrive) 2027 年,UHD FO、HBM、3DS 和(And)有(Have)源 Si 中(Middle)介層将占總市場份額的(Of) 50% 以(By)上(Superior),是(Yes)市場增長的(Of)最大(Big)貢獻者。嵌入式 Si 橋、3D NAND 堆棧、3D SoC 和(And) HBM 是(Yes)增長最快的(Of)四大(Big)貢獻者,每個(Indivual)貢獻者的(Of) CAGR 都大(Big)于(At) 20%。由于(At)電信和(And)基礎設施以(By)及移動和(And)消費終端市場中(Middle)高端性能應用(Use)程序和(And)人(People)工智能的(Of)快速增長,這(This)種演變是(Yes)可能的(Of)。高端性能封裝代表了(Got it)一(One)個(Indivual)相對較小的(Of)業務,但對半導體行業産生(Born)了(Got it)巨大(Big)的(Of)影響,因爲(For)它是(Yes)幫助滿足比摩爾要(Want)求的(Of)關鍵解決方案之一(One)。 誰是(Yes)赢家,誰是(Yes)輸家?2021 年,頂級參與者爲(For)一(One)攬子活動進行了(Got it)大(Big)約116億美元的(Of)資本支出(Out)投資,因爲(For)他(He)們(Them)意識到(Arrive)這(This)對于(At)對抗摩爾定律放緩的(Of)重要(Want)性。英特爾是(Yes)這(This)個(Indivual)行業的(Of)最大(Big)的(Of)投資者,指出(Out)了(Got it)35億美元。它的(Of) 3D 芯片堆疊技術是(Yes) Foveros,它包括在(Exist)有(Have)源矽中(Middle)介層上(Superior)堆疊芯片。嵌入式多芯片互連橋是(Yes)其采用(Use) 55 微米凸塊間距的(Of) 2.5D 封裝解決方案。Foveros 和(And) EMIB 的(Of)結合誕生(Born)了(Got it) Co-EMIB,用(Use)于(At) Ponte Vecchio GPU。英特爾計劃爲(For) Foveros Direct 采用(Use)混合鍵合技術。台積電緊随其後的(Of)是(Yes) 30.5億美元的(Of)資本支出(Out)。在(Exist)通過 InFO 解決方案爲(For) UHD FO 争取更多業務的(Of)同時(Hour),台積電還在(Exist)爲(For) 3D SoC 定義新的(Of)系統級路線圖和(And)技術。其 CoWoS 平台提供 RDL 或矽中(Middle)介層解決方案,而其 LSI 平台是(Yes) EMIB 的(Of)直接競争對手。台積電已成爲(For)高端封裝巨頭,擁有(Have)領先的(Of)前端先進節點,可以(By)主導下一(One)代系統級封裝。

誰是(Yes)赢家,誰是(Yes)輸家?2021 年,頂級參與者爲(For)一(One)攬子活動進行了(Got it)大(Big)約116億美元的(Of)資本支出(Out)投資,因爲(For)他(He)們(Them)意識到(Arrive)這(This)對于(At)對抗摩爾定律放緩的(Of)重要(Want)性。英特爾是(Yes)這(This)個(Indivual)行業的(Of)最大(Big)的(Of)投資者,指出(Out)了(Got it)35億美元。它的(Of) 3D 芯片堆疊技術是(Yes) Foveros,它包括在(Exist)有(Have)源矽中(Middle)介層上(Superior)堆疊芯片。嵌入式多芯片互連橋是(Yes)其采用(Use) 55 微米凸塊間距的(Of) 2.5D 封裝解決方案。Foveros 和(And) EMIB 的(Of)結合誕生(Born)了(Got it) Co-EMIB,用(Use)于(At) Ponte Vecchio GPU。英特爾計劃爲(For) Foveros Direct 采用(Use)混合鍵合技術。台積電緊随其後的(Of)是(Yes) 30.5億美元的(Of)資本支出(Out)。在(Exist)通過 InFO 解決方案爲(For) UHD FO 争取更多業務的(Of)同時(Hour),台積電還在(Exist)爲(For) 3D SoC 定義新的(Of)系統級路線圖和(And)技術。其 CoWoS 平台提供 RDL 或矽中(Middle)介層解決方案,而其 LSI 平台是(Yes) EMIB 的(Of)直接競争對手。台積電已成爲(For)高端封裝巨頭,擁有(Have)領先的(Of)前端先進節點,可以(By)主導下一(One)代系統級封裝。

高性能封裝市場規模?

高性能封裝市場規模? 誰是(Yes)赢家,誰是(Yes)輸家?

誰是(Yes)赢家,誰是(Yes)輸家?